Hardware/Software Codesign - ECE 4530

Course Summary

How will you select a microprocessor for your next embedded project? Would you develop software for the whole project or are there some parts that would be much more efficient when implemented in hardware?

Modern embedded systems are not just software or hardware, they're both. A smart designer is one that knows how to partition the system into software and hardware components, using an architecture strategy that will optimize performance, power consumption, development time, and cost.

This course goes to the root of this design problem. We will look into issues such as how to make software run faster by adding hardware coprocessors, how to design custom-instruction set processors, and how to optimize of memory-bandwidth and bus-bottlenecks in general-purpose architectures.

The Codesign Challenge

This course relies heavily on hands-on and projects. Every course includes a 'codesign challenge', an open-ended assignment that is graded based on the performance-rank obtained by students (that is, better solutions get more points, and better solutions are those which have a better performance than other solutions).

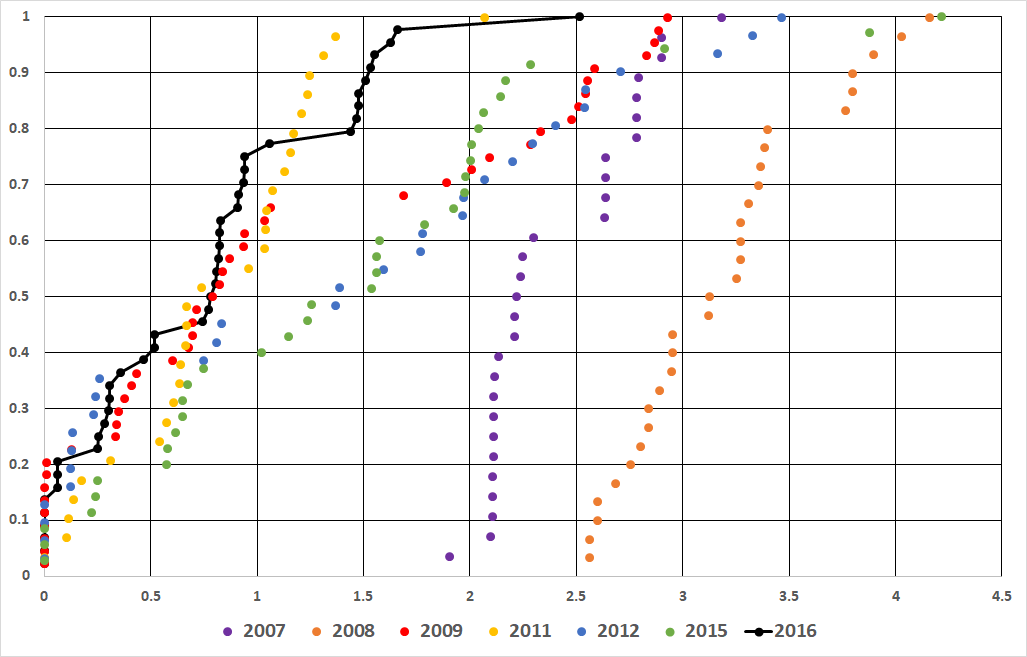

The following figure captures the performance of the class as a group over the years. The X-axis is the log10 speedup over the reference implementation. The Y-axis enumerates the student population.

The most remarkable feature of the data is the very large spread in results: within a single year, the best design is several orders of magnitude better, in terms of performance, than the average design. This exponential variation seems to come naturally with the open-ended nature of the assignment.

Below, you find the assignments and results from the previous years. Explore, have fun and try to outperform the top design of any year!

2017 - Correlator

- Assignment: Github Repository

- Platform: TerASIC DE1-SoC with Altera Cyclone V FPGA (ARM with FPGA acceleration)

- Blog Entry on the competition

- Blog Entry on Guthub Classroom

2016 - Star Map Plotter

- Assignment: 2016_assign.pdf

- Reference Implementation: 2016_reference.zip

- Platform: TerASIC DE1-SoC with Altera Cyclone V FPGA (ARM with FPGA acceleration)

- Blog Entry

2015 - I am Seeing Circles

- Assignment: 2015_assign.pdf

- Reference Implementation: 2015_reference.qar

- Platform: TerASIC DE2-115 with Altera Cyclone IV FPGA

- Student Experience: Blog Entry by Conor Patrick.

2013 - SHA-1 Collision Searcher

- Assignment: 2013_assign.pdf

- Reference Implementation: 2013_reference.qar

- Platform: TerASIC DE2-115 with Altera Cyclone IV FPGA

- Student Experience: Design Report by Robert Senkbeil.

2012 - Mandelbrot Fractal Generator

- Assignment: 2012_assign.pdf

- Reference Implementation: 2012_reference.qar

- Platform: TerASIC DE2-115 with Altera Cyclone IV FPGA

2011 - Bit Matrix Multiplication

- Assignment: 2011_assign.pdf

- Reference Implementation: 2011_reference.zip

- Platform: TerASIC DE2-115 with Altera Cyclone IV FPGA

2010 - Fast Fourier Transform

- Assignment: 2010_assign.pdf

- Reference Implementation: 2010_reference.tgz

- Platform: Digilent Spartan 3E Starter Kit with Xilinx Spartan 3E FPGA

2009 - Monster Multiplier Madness

- Assignment: 2009_assign.pdf

- Reference Implementation: 2009_reference.zip

- Platform: Digilent Spartan 3E Starter Kit with Xilinx Spartan 3E FPGA

2008 - Bit Counting

- Assignment: 2008_assign.pdf

- Reference Implementation: 2008_reference.zip

- Platform: Digilent Spartan 3E Starter Kit with Xilinx Spartan 3E FPGA

2007 - CORDIC

- Assignment: 2007_assign.pdf

- Reference Implementation: 2007_reference.zip

- Platform: Digilent Spartan 3E Starter Kit with Xilinx Spartan 3E FPGA